超簡単・FET差動アンプを LTSpice でシミュレート

|

DAC基板のユーザ様から 「超簡単・FET式差動ラインプリアンプ」 の

ご紹介を受けました。 初めて見る回路だったので LTSpice で

解析してみることにしました。

|

差動プリについての 原典 は

「 FET式 差動アンプ 超簡単・超廉価 」

で 検索してみて下さい。 ぺるけ式 と呼ばれることもあるようです。 すぐ見つかります。

尚、シミュレートするにあたり 原典の解説は 殆ど読んでおりませんので 悪しからず。 |

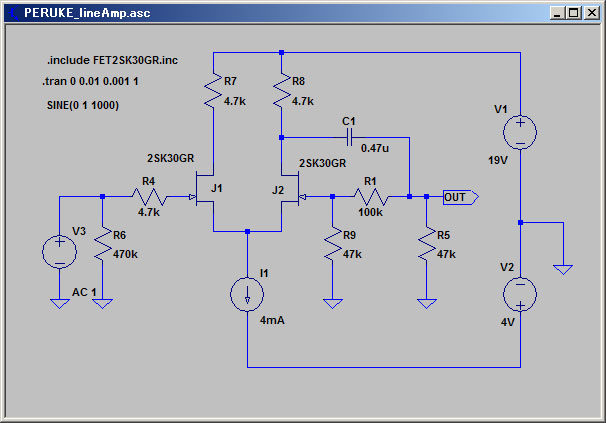

こんな感じの回路です

←クリック ←クリック

初めて見ると、かなり違和感がありますが ・ ・ ・ ・ ・

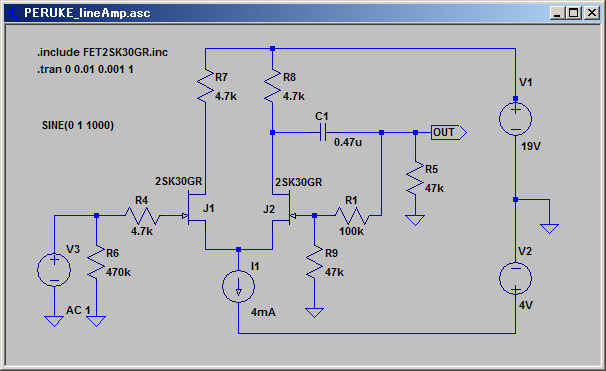

若干 書き換えてみると、違和感が少なくなります

な〜るほど ・ ・ ・

|

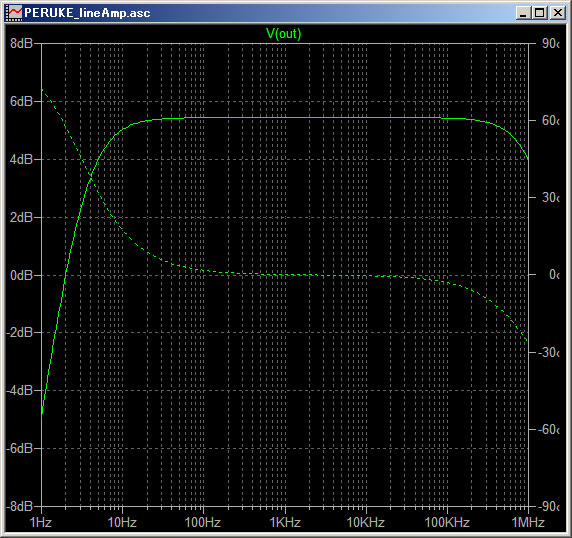

では早速、周波数特性を見てみます

・説明によると、この回路は 6dBゲインとのことですが 若干少なめの結果です。

・低域特性から、出力コンデンサ 0.47uFは 少し小さいような気もします。

・高域の位相は、100KHzでも殆どまわってないので 安定した回路といえそうです。 |

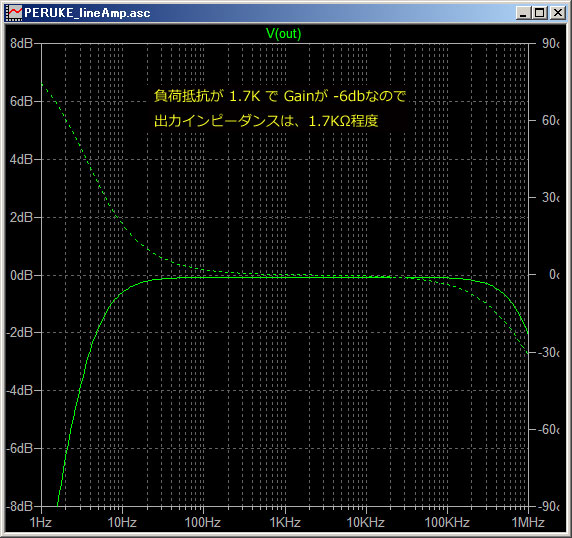

次に出力インピーダンスを見てみます

・出力端の負荷抵抗(R5)を変えて、ゲインが-6dBになる点を探します。

・1.7KΩでゲイン0dBでしたから、出力インピーダンスは 大凡 1.7KΩです。

*(注)出力のカップリングコンデンサ(C1)は、4.7uFに変えてます。 |

|

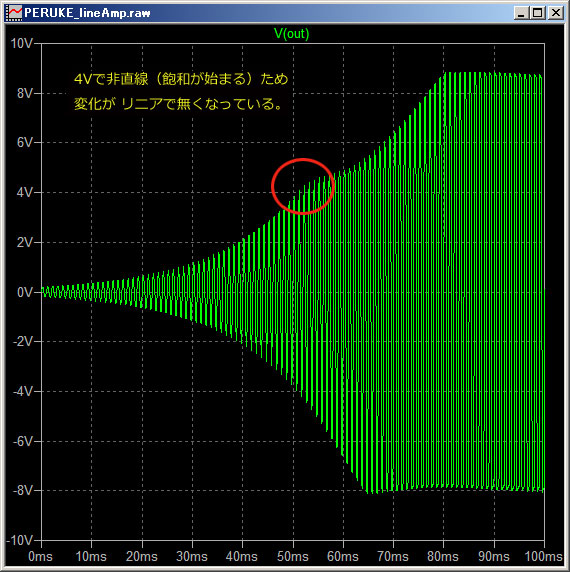

つぎに、出力の振幅幅を見てみます

・この波形は、1KHzの入力電圧を 徐々に大きくしていった時のものです

・最大出力は、16Vpp (5.6Vrms) ぐらい 得られそうですが ・ ・ ・

・4Vp付近で こぶみたいになって、リニアに出力が変化してないことがわかります。 |

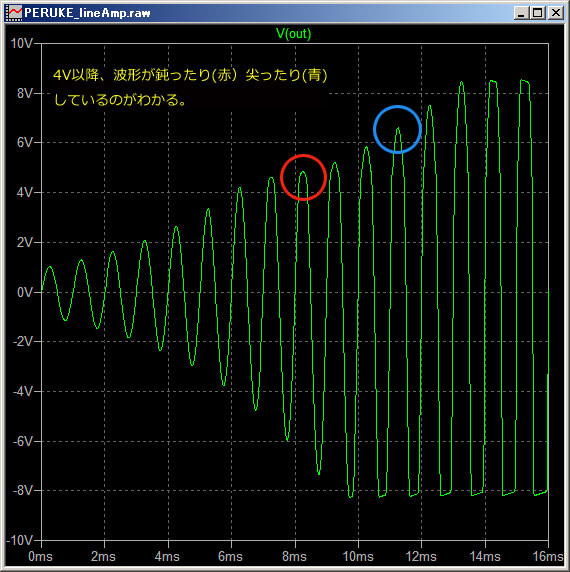

拡大すると ・ ・ ・

・4Vを超えたところで、波形がつまり気味になり 6Vを超えると逆にとんがります。

・どうやら、この回路の実用的な 出力範囲は 4Vp (2.8Vrms) 程度と見るのが

妥当なようです |

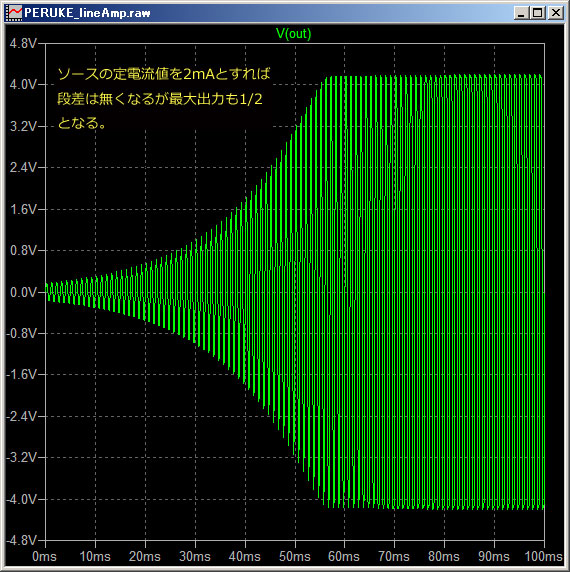

動作点を変えて上下対称になる点を探してみました

・出力の振幅波形が、上下対称になる点を探してみました

・単純に、ソースに入っている 定電流源(CRD)を振っただけですが

・小さくしていくと、振幅波形の上下が対象になるようです。

・2mAで 段差が無くなるようですが、最大出力も 4Vp まで落ちますので、

あまり 意味無いようです。

・どうやら、FET 2石で 電源利用率を高めるのは苦しそうです。

( 電源電圧 -4V と 動作点の見直しから ・ ・ ・ ですネ )

回路設定の最適点は他にあるのかも知れませんが、今回はこの辺で。

実際に使って見る時に 「深追い」 してみましょう

|

お断り : シミュレートするにあたり 原典の解説は 殆ど読んでおりませんので 悪しからず。

|